Duration: 18 months

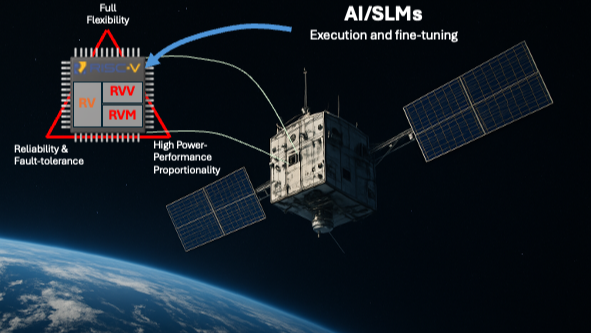

This project aims to design, prototype, and evaluate a reliable, energy-efficient, and time-predictable RISC-V processor tailored for the execution and fine-tuning of embedded Small Language Models (SLMs) on resource-constrained space-grade edge computing platforms. Modern SLMs can dramatically enhance autonomy, resilience, and in-orbit decision-making capabilities in satellite missions, but their deployment is currently constrained by the limited performance, programmability, and reliability of existing space-qualified hardware. Our approach introduces a novel, reliable vector-matrix processor built on the open-source RISC-V Vector Instruction Set Architecture (ISA), augmented with a fault-tolerant Tensor Processing Unit (TPU). A key differentiator lies in the integration of AI acceleration capabilities directly within the ISA, achieved through a set of RISC-V matrix extensions currently under standardization by the RISC-V community. This design choice ensures programmability while avoiding vendor lock-in. The proposed processor is optimized for the efficient execution of AI workloads, leveraging low-precision and mixed-format arithmetic. Moreover, the architecture supports on-demand hardware reliability features, enabling dynamic trade-offs between fault-tolerance and performance. The project includes RTL design, physical implementation down to a silicon-ready layout in advanced technology nodes (e.g., TSMC N7), FPGA-based functional prototyping, and comprehensive benchmarking against state-of-the-art AI solutions. All outcomes will be released open-source to accelerate industrial uptake and foster further research. This work will provide a foundational building block for European open hardware ecosystems, enabling a new generation of autonomous, AI-enabled space missions, while also offering cross-sector applicability in aerospace, defense, and industrial edge AI domains.