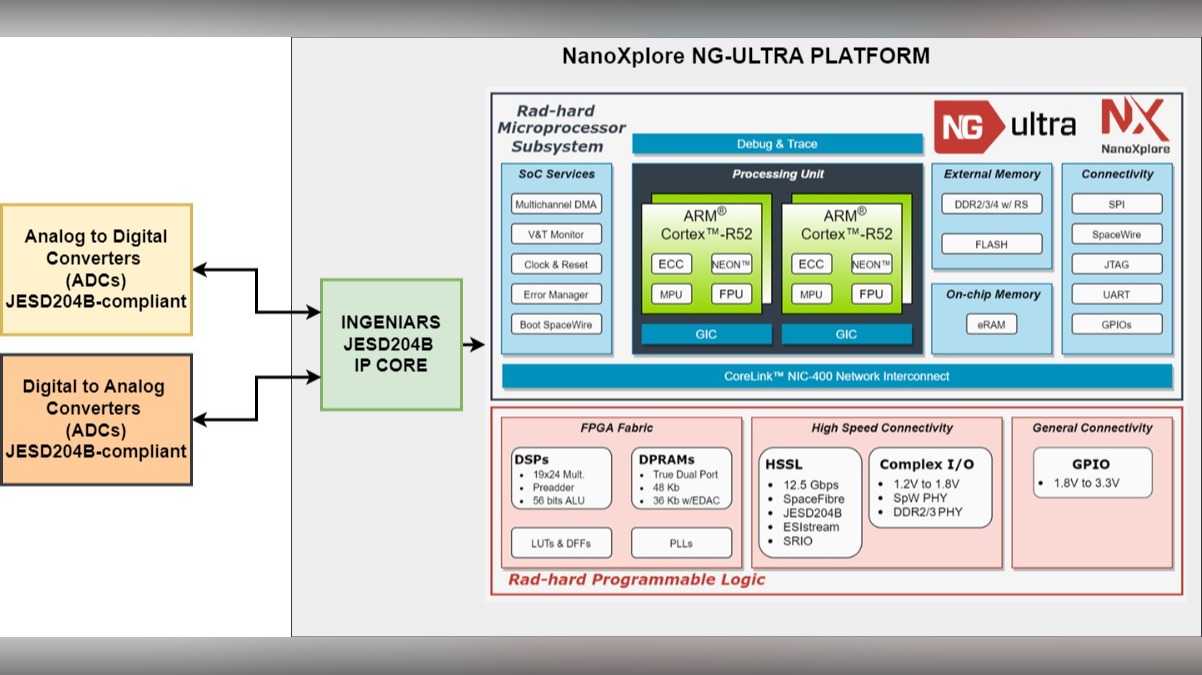

In space telecommunications, very high-speed interfaces are essential because they enable quick, large-volume data transfer between spacecraft, satellites, and base stations. High-speed digital-to-analog converters (DACs) and analog-to-digital converters (ADCs) able to handle sample rates in the order of tents of GHz are available on the market and can be used in combination with HW accelerators such as FPGAs device to implement high-performance communication systems. Such converters transfer samples acquired by the ADC toward the FPGA or samples generated by the FPGA toward the DAC through an interface that is based on JESD204B/C standard. An FPGA IP Core implementing such standard is still not available for the European NanoXplore NG Ultra FPGA, not enabling this technology to be used to develop telecommunication systems as well as the possibility to implement digital beamforming for radar systems. The main objective of this activity is to design, develop and validate an Intellectual Property (IP) Core implementing the JESD204B/C high-speed serial communication protocol. The IP Core will be implemented in technology independent VHDL language, and the target technology for the characterization and validation will be the NanoXplore NG-ULTRA FPGA platform. The activity will start the design of the Data-Link Layer defined by the JESD204B/C standard and it will continue with the development in VHDL and with the functional verification. The second phase of the project will focus on characterization on target FPGA. The activity will be concluded with the hardware validation, implementing a test setup with the IP core integrated within the FPGA and connected to data converters, both ADC and DAC demonstrating the communication through the JESD204B/C protocol between the converters and the FPGA. A proper configuration of the IP Core will be identified in accordance with the target data converters selected for the validation.