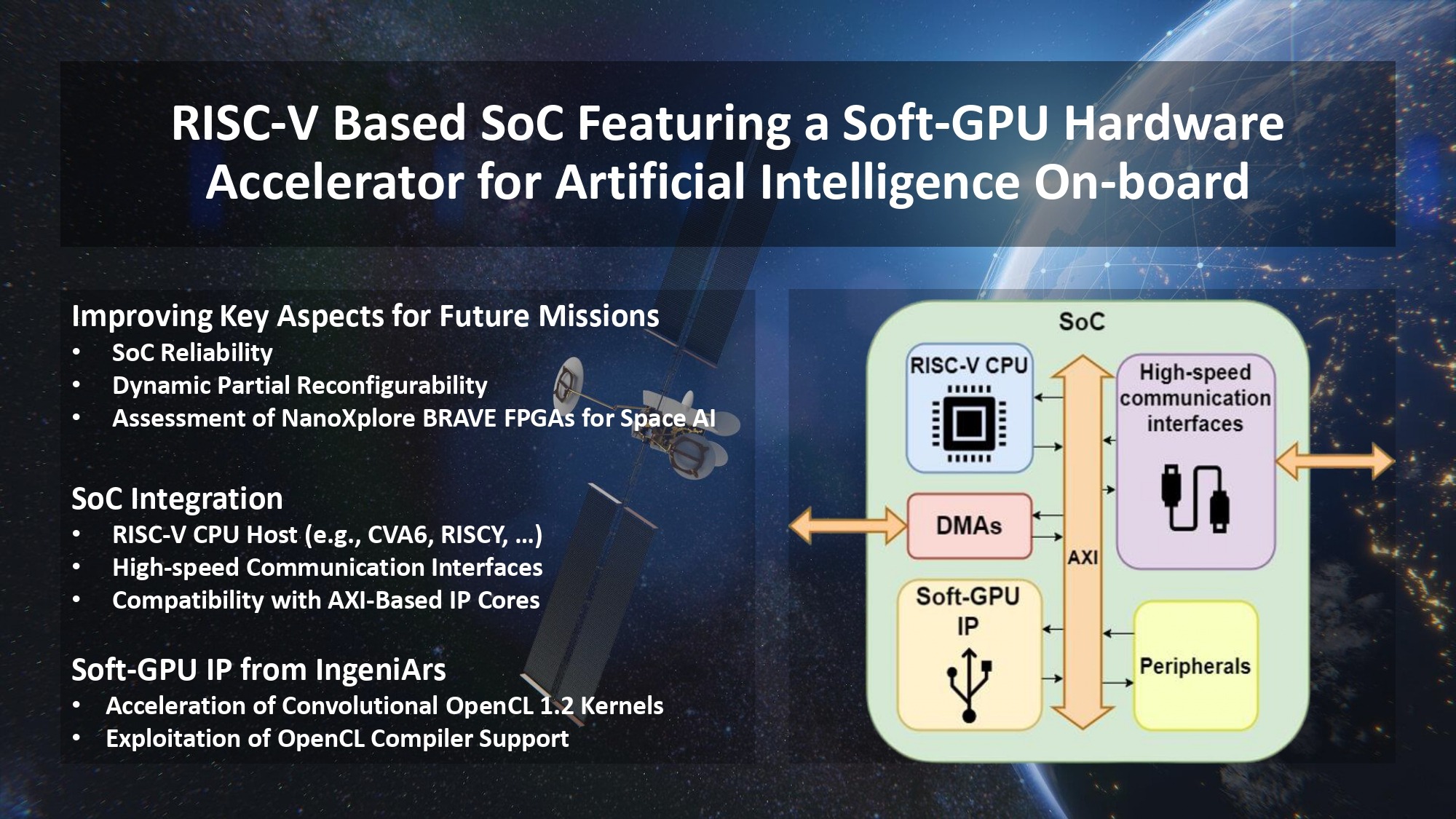

In recent years, Machine Learning (ML) algorithms have become extremely widespread in many sectors thanks to their flexibility and adaptability. However, ML is still far from being consistently used in space applications. General-Purpose Computing on Graphic Processing Units (GPGPU) could help to improve the State-of-the-Art for AI acceleration by providing a platform that can be programmed through dedicated frameworks (e.g., OpenCL) and implemented even on Space-Grade FPGAs. Therefore, the research aims to develop a SoC overlay featuring a RISC-V CPU, a GPU-like architecture as hardware accelerator and high-speed communication interfaces to run OpenCL 1.2 kernels on FPGA. The proposal will be built on top of existing and available IPs: the RISC-V CPU can be chosen among the various openly available (e.g., CVA6, RISCY); the GPU-like IP will be based on the soft-GPU IP developed by IngeniArs. To further improve the product usability in terms of reliability, power consumption and speed performance, the idea is to develop an entirely innovative platform, providing the community with a system that could be used in future space missions. Our efforts will also take into account the ESA Advanced Data Handling Architecture (ADHA) initiative, designing a compatible system. In particular, we will focus on: investigating mitigation techniques to enhance SoC robustness (e.g., partial-TMR), trading off impact on power consumption, processing speed and design complexity; implementing partial reconfigurability, allowing area/power complexity trade-offs and recovery from potential failures. In addition, we plan to provide results using benchmarks like GPU4S or OBPMark to compare performance-per-power metrics. Implementation on BRAVE FPGAs will be considered, helping the assessment of these novel European devices for AI applications. This idea has already gained interest from industry (Thales, IngeniArs, Sitael, AIKO, ResilTech), as well as internal support from ESA staff members.