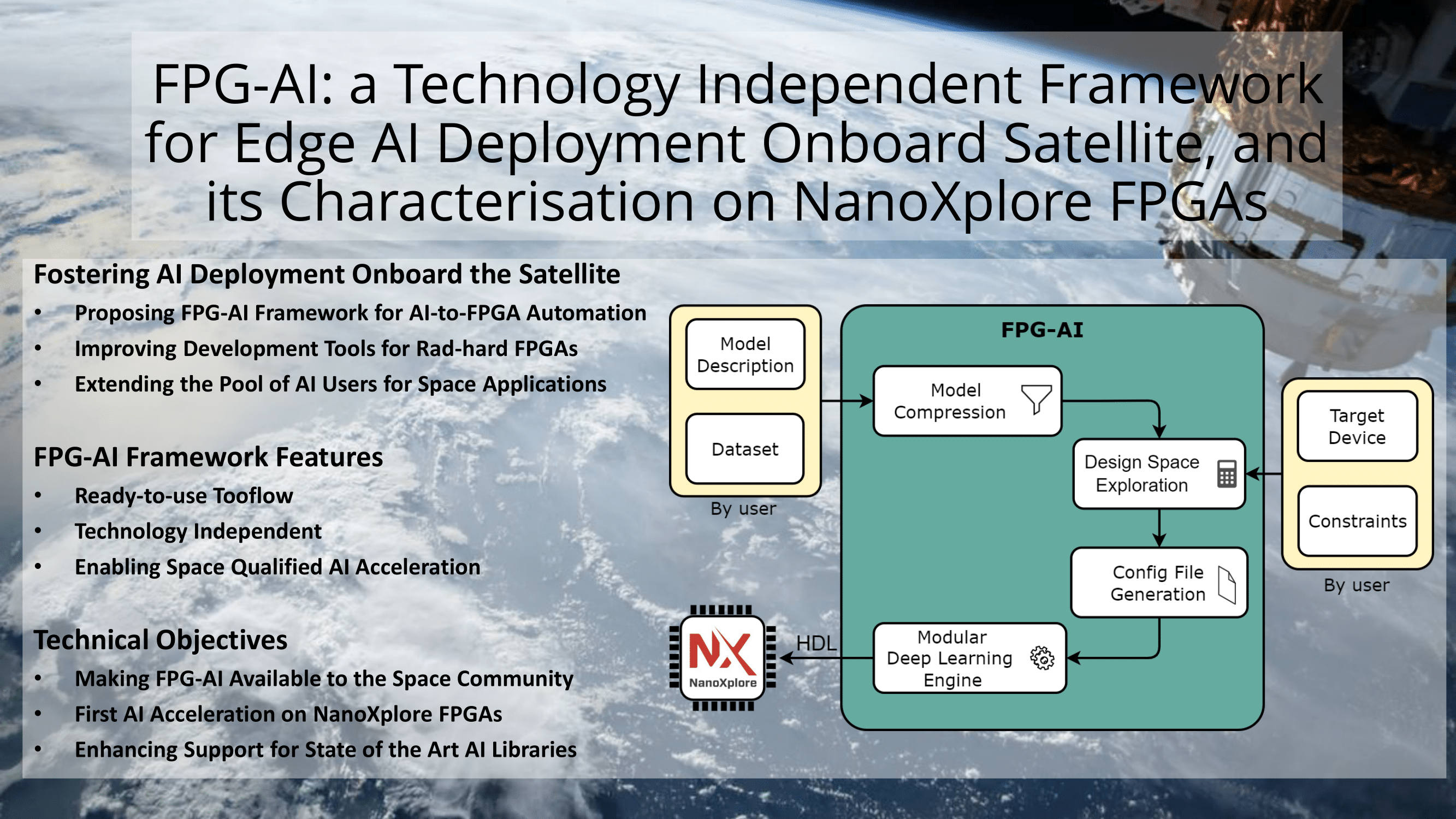

In recent years, research in the space community has shown a growing interest in AI, mostly driven by systems miniaturization and commercial competition[1]. FPGAs have proven to be competitive accelerators for these algorithms and works proposing methods for automating the design on these devices have acquired relevance [2]. The common purpose is to enable a wide range of users without specific skills to accelerate AI models on FPGAs with reduced development times. Among the emerging frameworks, FPG-AI constitutes a valuable option for promoting the deployment of AI onboard the satellite. The foundations (TRL2) of this toolflow have been developed with a previous research activity between ESA and the University of Pisa [3].

Unlike other solutions, FPG-AI is not a vendor-specific flow and does not pose technology limits on the characterization (inference time, resources, power) of AI accelerators. In addition, the framework features a fully-handcrafted and human-readable HDL with no third-party IPs, thus facilitating code explicability, reliability, and space qualification. FPG-AI provides as output the HDL sources of the accelerator and not the final bitstream, allowing the user to exploit the unused portion of the FPGA for complementary tasks. The main objectives of this project are to reach TRL4 of FPG-AI and make it available to the space community.

This will be done by:

- Extending and consolidating the framework to a wider set of supported AI algorithms, e.g. Recurrent Neural Networks (RNNs), providing hardware characterization of AI-based space applications such as FDIR or Telemetry Forecasting.

- Ensuring that all state-of-the-art devices are supported by the tool, especially focusing NanoXplore FPGAs, enabling the use of these devices for AI applications and pursuing European sovereignty.

- Evaluating the tool capability with a prototype hardware demonstrator. This idea has already gained interest from industry (NanoXplore,Thales,Sitael,IngeniArs,Aiko).

_____

- Gianluca Giuffrida et al. “The Φ-Sat-1 Mission: The First On-Board Deep Neural Network Demonstrator for Satellite Earth Observation”. In: IEEE Transactions on Geoscience and Remote Sensing 60 (2022), pp. 1–14. https://doi.org/10.1109/TGRS.2021.3125567

- Stylianos I. Venieris, Alexandros Kouris, and Christos-Savvas Bouganis. “Toolflows for Mapping Convolutional Neural Networks on FPGAs: A Survey and Future Directions”. In: ACM Comput. Surv. 51.3 (June 2018). issn: 0360-0300. https://doi.org/10.1145/3186332

- Emilio Rapuano, Luca Fanucci, and Dario Izzo. "A novel design framework for rapid and efficient Artificial Intelligence deployment for on-board space applications". Contract Number: 4000129792/20/NL. 2018

- Rapuano E., Pacini T., Fanucci L. "A Post-training Quantization Method for the Design of Fixed-Point-Based FPGA/ASIC Hardware Accelerators for LSTM/GRU Algorithms"

(2022) Computational Intelligence and Neuroscience, 2022, art. no. 9485933 - Pacini T., Rapuano E., Dinelli G., Fanucci L. "A multi-cache system for on-chip memory optimization in fpga-based cnn accelerators" (2021) Electronics (Switzerland), 10 (20), art. no. 2514

- Comino C., Pacini T., Rapuano E., Fanucci L. "Design and Implementation of an FPGA-Based CNN Hardware Accelerator Using Partial Reconfigurability: The CloudScout Case Study" (2022) Lecture Notes in Electrical Engineering, 866 LNEE, pp. 187 - 193

- Rapuano, E.; Meoni, G.; Pacini, T.; Dinelli, G.; Furano, G.; Giuffrida, G.; Fanucci, L. "An FPGA-Based Hardware Accelerator for CNNs Inference on Board Satellites: Benchmarking with Myriad 2-Based Solution for the CloudScout Case Study." Remote Sens.2021, 13, 1518. https://doi.org/10.3390/rs13081518

- G. Dinelli, G. Meoni, E. Rapuano, T. Pacini and L. Fanucci, "MEM-OPT: A Scheduling and Data Re-Use System to Optimize On-Chip Memory Usage for CNNs On-Board FPGAs," in IEEE Journal on Emerging and Selected Topics in Circuits and Systems, vol. 10, no. 3, pp. 335-347, Sept. 2020, doi: 10.1109/JETCAS.2020.3015294.

- Nannipieri, P., Giuffrida, G., Diana, L., Panicacci, S., Zulberti, L., Fanucci, L., ... & Hubner, M. (2022, March) "ICU4SAT: A General-Purpose Reconfigurable Instrument Control Unit Based on Open Source Components". In 2022 IEEE Aerospace Conference (AERO) (pp. 1-9). IEEE. https://doi.org/10.1109/AERO53065.2022.9843414

- Zulberti, L., Monopoli, M., Nannipieri, P., & Fanucci, L. (2022, June). "Architectural Implications for Inference of Graph Neural Networks on CGRA-based Accelerators". In 2022 17th Conference on Ph. D Research in Microelectronics and Electronics (PRIME) (pp. 373-376). IEEE. https://doi.org/10.1109/PRIME55000.2022.9816810

- Nannipieri, P., Di Matteo, S., Zulberti, L., Albicocchi, F., Saponara, S., & Fanucci, L. (2021). "A RISC-V Post Quantum Cryptography Instruction Set Extension for Number Theoretic Transform to Speed-Up CRYSTALS Algorithms". IEEE Access, 9, 150798-150808. https://doi.org/10.1109/ACCESS.2021.3126208

- Zulberti, L., Nannipieri, P., & Fanucci, L. (2021, June). A script-based cycle-true verification framework to speed-up hardware and software co-design of system-on-chip exploiting RISC-V architecture. In 2021 16th International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS) (pp. 1-6). IEEE. https://doi.org/10.1109/DTIS53253.2021.9505139

- Nannipieri, P., Di Matteo, S., Baldanzi, L., Crocetti, L., Zulberti, L., Saponara, S., & Fanucci, L. (2021). "VLSI design of Advanced-Features AES CryptoProcessor in the framework of the European Processor Initiative". IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 30(2), 177-186. https://doi.org/10.1109/TVLSI.2021.3129107

- Giuffrida G, Diana L, de Gioia F, Benelli G, Meoni G, Donati M, Fanucci L. "CloudScout: A Deep Neural Network for On-Board Cloud Detection on Hyperspectral Images". Remote Sensing. 2020; 12(14):2205. https://doi.org/10.3390/rs12142205

- P. Nannipieri, G. Dinelli, D. Davalle and L. Fanucci, "A SpaceFibre multi lane codec System on a Chip: enabling technology for low cost satellite EGSE," 2018 14th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), 2018, pp. 173-176, doi: 10.1109/PRIME.2018.8430317.

- G. Dinelli, G. Meoni, E. Rapuano and L. Fanucci, "Advantages and Limitations of Fully on-Chip CNN FPGA-Based Hardware Accelerator," 2020 IEEE International Symposium on Circuits and Systems (ISCAS), 2020, pp. 1-5, doi: 10.1109/ISCAS45731.2020.9180867.

- Gianmarco Dinelli, Gabriele Meoni, Emilio Rapuano, Gionata Benelli, Luca Fanucci, "An FPGA-Based Hardware Accelerator for CNNs Using On-Chip Memories Only: Design and Benchmarking with Intel Movidius Neural Compute Stick", International Journal of Reconfigurable Computing, vol. 2019, Article ID 7218758, 13 pages, 2019. https://doi.org/10.1155/2019/7218758

- Gianmarco Dinelli, Pietro Nannipieri, Antonino Marino, Luca Fanucci, Luca Dello Sterpaio, "The very high-speed SpaceFibre multi-lane CoDec: Implementation and experimental performance evaluation," Acta Astronautica, Volume 179, 2021, Pages 462-470, ISSN 0094-5765, https://doi.org/10.1016/j.actaastro.2020.11.028.

- Pietro Nannipieri, Gianmarco Dinelli, Antonino Marino, Luca Dello Sterpaio, Alessandro Leoni, Luca Fanucci, Daniele Davalle, "A serial high-speed satellite communication CODEC: Design and implementation of a SpaceFibre interface," Acta Astronautica, Volume 169, 2020, Pages 206-215, ISSN 0094-5765, https://doi.org/10.1016/j.actaastro.2020.01.010.

- Antonino Marino, Alessandro Leoni, Luca Dello Sterpaio, Pietro Nannipieri, Gianmarco Dinelli, Gionata Benelli, Daniele Davalle, Luca Fanucci, "SpaceART SpaceWire and SpaceFibre Analyser Real-Time," 2020 IEEE 7th International Workshop on Metrology for AeroSpace (MetroAeroSpace), 2020, pp. 244-248, doi: 10.1109/MetroAeroSpace48742.2020.9160319.

- G. Furano et al., "Towards the Use of Artificial Intelligence on the Edge in Space Systems: Challenges and Opportunities," in IEEE Aerospace and Electronic Systems Magazine, vol. 35, no. 12, pp. 44-56, 1 Dec. 2020, doi: 10.1109/MAES.2020.3008468.

- Dinelli G., Meoni G., Nannipieri P., Dello Sterpaio L., Marino A., Fanucci L. (2020) "Integration of a SpaceFibre IP Core with the LEON3 Microprocessor Through an AMBA AHB Bus." In: Saponara S., De Gloria A. (eds) Applications in Electronics Pervading Industry, Environment and Society. ApplePies 2019. Lecture Notes in Electrical Engineering, vol 627. Springer, Cham. https://doi.org/10.1007/978-3-030-37277-4_58

- Gabriele Meoni, Riccardo Cassettari, Matteo Bertolucci, Antonino Marino, Daniele Davalle, Marco Trafeli, Luca Fanucci, "CCSDS 131.2-B-1 telemetry transmitter: A VHDL IP core and a validation architecture on board RTG4", FPGA, Acta Astronautica, Volume 176, 2020, Pages 484-493, ISSN 0094-5765, https://doi.org/10.1016/j.actaastro.2020.06.036.