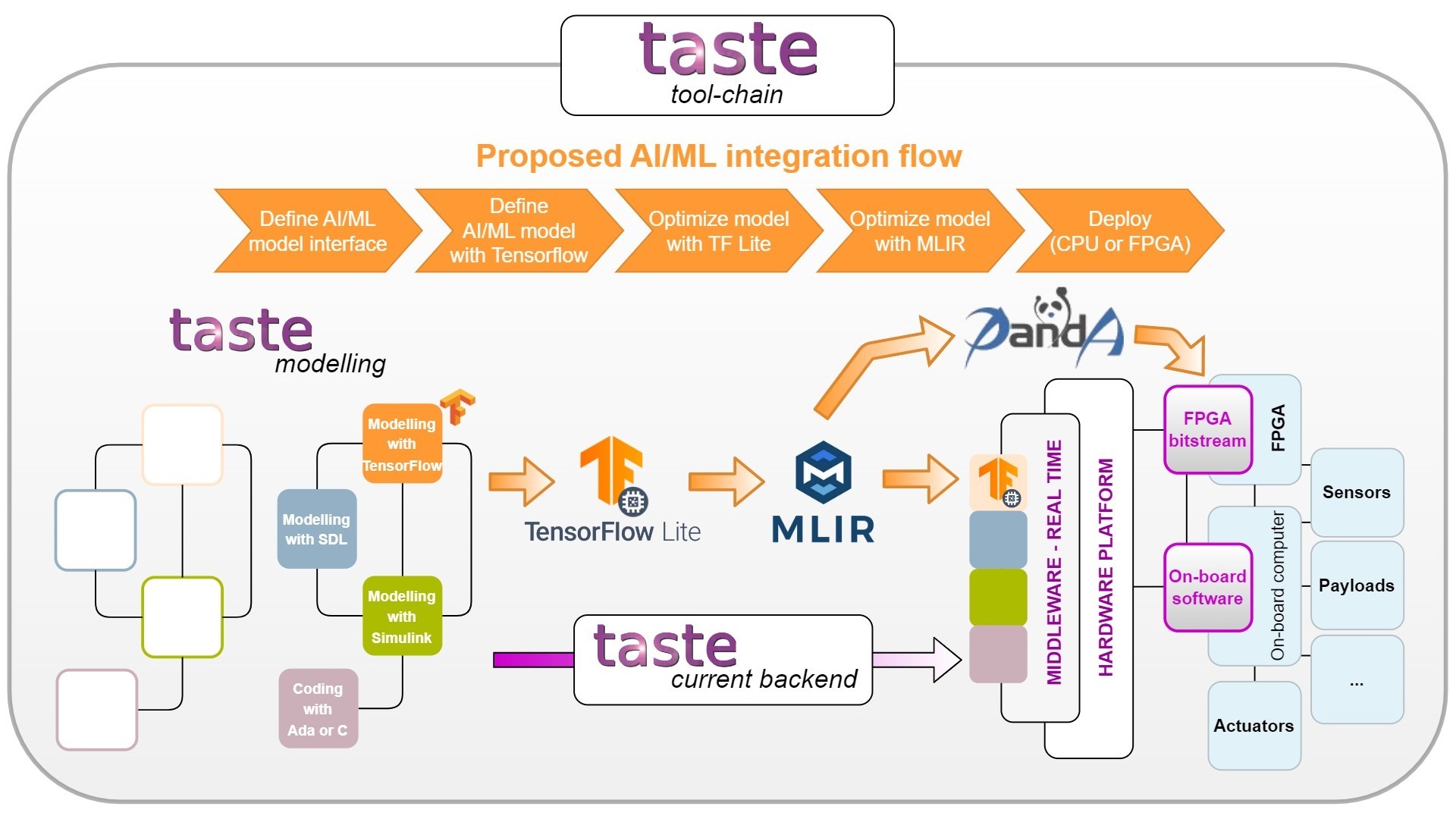

TASTE is an open-source set of tools targeting Model-Based development of real-time systems that integrate all design, development, and deployment steps. It offers a set of independent tools and a development process that links together several existing technologies, rather than creating a new modeling language that would have to satisfy different properties in different stages of development. Following the TASTE concept, the proposed idea is to integrate the Machine Learning set of tools offered by TensorFlow Lite into the TASTE toolchain. This is going to extend TASTE the already present support for external modeling tools such as OpenGeode and Matlab Simulink to the novel Machine Learning applications. TensorFlow Lite can be leveraged to generate ML code blocks targeting low resource power-efficient microcontrollers within a heterogeneous system while still being able to rely on the solid base of model-based development techniques offered within the TASTE toolchain. Further integration of the open-source PandA Bambu High-Level Synthesis tool is also interesting to extend the capability of the generated ML code blocks to FPGA targets too. PandA Bambu HLS is an open-source framework featuring a high-level synthesis flow that generates RTL designs starting from C/C++ software descriptions. As the Tensorflow Lite toolchain generates C code for microcontrollers, its output can be easily fed into the high-level synthesis flow to generate ML hardware accelerators. The proposed idea aims at the following objectives: - extending the TASTE toolchain to support Machine Learning blocks through the integration of TensorFlow Lite - integrate Machine Learning techniques within a Model-Based development flow linking the best from both worlds - add support for automated hardware acceleration of Machine Learning applications through High-Level Synthesis on FPGA platforms - exploit High-Level Synthesis to generate power-efficient radiation-hardened accelerator designs for Machine Learning