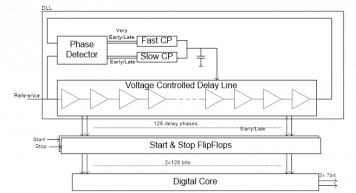

Time-to-Digital Converters (TDCs) are crucial elements in many sensor readout systems, such as time-of-flight sensors, laser ranging devices, LiDAR, ultrasonic sensors, particle detectors, etc. To the best of our knowledge, there is currently no rad-hard TDC component available on the market, which could meet the targeted specification defined in this project. Current radiation tolerant TDCs are mostly based on radiation tolerant FPGAs with a resolution of around 100 ps and radiation tolerance up to merely 10 kGy. FPGA based TDCs suffer from high power consumption, high implementation cost, large device size, and limited resolution. In this project, we propose to develop a radiation-hardened TDC in a mainstream commercial CMOS process using radiation-hardening-by-design (RHBD) techniques, which offers highest integration level, lowest power consumption, and lower fabrication cost for volume production. The goal of this project is designing, prototyping and lab testing of a radiation-hardened single-chip picosecond TDC in a commercial 65 nm CMOS technology. The TDC will be able to measure time differences between a start and stop signal and convert this to a digital value with an accuracy better than 10 picoseconds. It will support ‘single shot’ operation, which means it can carry out the conversion with the proposed accuracy even from a single start and stop signal, without averaging or noise shaping. The proposed TDC shall achieve a total-ionizing-dose (TID) tolerance of more than 100 kGy, and single event latch-up and upset immune up to an LET of 100 MeV·cm2/mg, which makes it suitable for applications in space, nuclear, medical accelerators, and avionics.